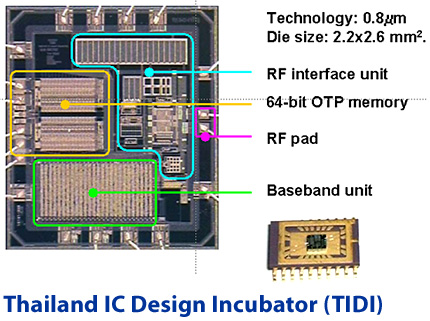

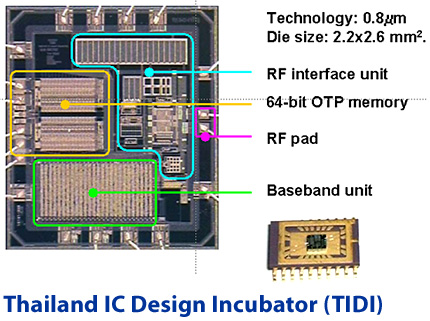

In addition, we have developed various kinds of CMOS integrated circuits including Digital CMOS, Analog/Mixed Signal (AMS) CMOS, CMOS technology that consumes low level of electricity, MEMS technology, Power MOS technology, System-on-Chip (SOC) technology, and Advance IC Packaging technology that serve specific operations or the operation of integrated circuits that has high level of capacity and is very complicated.

Document

ˇŇĂÍ͡Ẻǧ¨ĂĂÇÁ (IC Fabrication)

ǧ¨ĂĂÇÁ (IC) ąŃéąÁŐ˘Ń鹵͹ˇŇþѲąŇÍÂŮč 2 ĘčÇą ä´éáˇčĘčÇą˘Í§ˇŇĂÍ͡Ẻ áĹĐĘčÇą˘Í§ˇŇĂĽĹÔµµŇÁ·ŐčˇĹčŇǢéҧµéą ăą´éŇąˇŇĂÍ͡ẺąŃéą´ÓŕąÔąˇŇĂâ´Â§ŇąÇÔ¨ŃÂÍ͡Ẻǧ¨ĂĂÇÁ áĹĐăąĘčÇą˘Í§ˇŇĂĽĹÔµąŃéą´ÓŕąÔąˇŇĂâ´ÂČŮąÂěäÁâ¤ĂÍÔŕĹ硷ĂÍąÔˇĘě (TMEC) áĹĐâç§ŇąĽĹԵ㹵čҧ»ĂĐŕ·Č ÇÔ¸ŐˇŇĂÍ͡Ẻǧ¨ĂĂÇÁ¨ĐÁŐ·Ńé§áşş´Ô¨µÍĹĹéÇąć (Digital IC design) ËĂ×ÍáşşÍĐąŇĹç͡ĹéÇąć (Analog IC design) ËĂ×ÍĂÇÁ·Ńé§ĘͧẺăąŕÇĹŇŕ´ŐÂǡѹ (Mixed signal IC design) 㹡óշŐčĂĐşşÁŐ¤ÇŇÁ«Ńş«éÍąĘ٧ˇŇĂÍ͡ẺÍҨăŞéŕ·¤ąÔ¤ system-on-chip design ·Ń駹Őé㹢Ń鹵͹ˇŇĂÍ͡ẺäÍ«Őâ´Â·ŃčÇä»ĘŇÁŇöáĘ´§ä´é´Ń§ĂŮ»

Design Entry

ĽŮéÍ͡ẺŕĂÔčÁµéą´éÇ¡ŇáÓËą´ĂŇÂĹĐŕÍŐ´˹éŇ·ŐčˇŇ÷ӧҹ˘Í§Ç§¨ĂĂÇÁ·Ő赹µéͧˇŇĂ áĹéÇ»éÍąĂŇÂĹĐŕÍŐ´ąŐéŕ˘éŇĘŮč¤ÍÁľÔÇŕµÍĂě «Öč§ĘŇÁŇö·Óä´éâ´ÂˇŇĂÇҴἹŔŇľŕ¤éŇĂčҧ (schematic) ˘Í§Ç§¨Ăâ´ÂµĂ§ ËĂ×Íâ´ÂˇŇĂĘĂéҧâ»ĂáˇĂÁăąŔŇÉŇľĂĂłąŇÎŇĂě´áÇĂě (Hardware Description Language: HDL) ŕŞčąŔŇÉŇ VHDL áĹĐŔŇÉŇ Verilog áĹéÇăËé¤ÍÁľÔÇŕµÍĂě·ÓˇŇĂĘѧŕ¤ĂŇĐËě (synthesis) ἹŔŇľŕ¤éŇĂčҧăËé ˇŇĂÍ͡Ẻ㹢ŃéąąŐéŕĂŇĘąă¨ŕľŐ§ľÄµÔˇĂĂÁ˘Í§ĂĐşş·ŐčŕĂŇÍ͡Ẻŕ·čŇąŃéą

ĂŮ»µŃÇÍÂčҧˇŇĂÍ͡Ẻâ´ÂăŞéŔŇÉŇ VHDL áĹéÇĘѧŕ¤ĂŇĐËěŕ»çąĹͨԡࡵ

Simulation

ĽŮéÍ͡ẺąÓ schematic ÁŇ·ÓˇŇèÓĹͧˇŇ÷ӧҹ (simulation) ŕľ×č͵ĂǨĘÍş¤ÇŇÁ¶Ůˇµéͧ˘Í§Ç§¨Ă·ŐčÍ͡ẺµŇÁ˘éÍÁŮĹăąŕǡŕµÍĂě·´ĘÍş (test vector) ·ŐčĽŮéÍ͡ẺˇÓËą´äÇé â´ÂľÔ¨ŇóҨҡä´ÍĐáˇĂÁ·Ň§ŕÇĹŇ (timing diagram) áĹСŇèÓĹͧ¤ÇŇÁĽÔ´ľĹŇ´·ŐčŕˇÔ´˘Öéą ĽĹ¨Ňˇ simulation ¨Đ¶ŮˇăŞé㹡ŇĂ»ĂŃş»Ăاáˇéä˘Ç§¨ĂăËé¶Ůˇµéͧ ˇčÍąˇŇĂÍ͡ẺĽŃ§Ç§¨Ă㹢Ń鹵͹ĘŘ´·éŇÂ

Physical Layout

ĽŮéÍ͡ẺąÓἹŔŇľŕ¤éŇĂčҧ (schematic) ÁŇá»Ĺ§ăËéŕ»çąĽŃ§ŔŮÁÔǧ¨Ă (layout) ĂĐ´ŃşˇŇÂŔŇľ «Ö觨ĐăŞéŕ»çąáşş·Őč¨Đ¶Ůˇ¶čŇ·ʹŧşąáĽčąŕÇŕżÍĂě (áÇ蹼ĹÖˇ˘Í§ĘŇáÖ觵ŃÇąÓ«ÔĹԡ͹) ·ŐčŕµĂŐÂÁŕ˘éҡĂкǹˇŇĂŕ¨×ÍĘŇĂăËéŕ»çąáĽčąÇ§¨ĂĂÇÁ·Őč¨Đ¶ŮˇµŃ´áşč§ŕ»çąŞÔ»ËĹҵŃǵčÍä»

ˇŇĂÍ͡ẺĽŃ§Ç§¨ĂÁŐ 2 ÇÔ¸ŐËĹŃˇć ¤×Í

- ĂĐşş Pre-Treatment ŕ»çąĂĐşşˇŇĂ·Ó¤ÇŇÁĘĐÍŇ´ąéÓŕş×éͧµéą ŕľ×čÍ»ĂŃşąéÓ´Ôş·ŐčÁŐ¤ÇŇÁˇĂĐ´éҧ»Đ»ąÍÂŮčăËéŕ»çąąéÓÍčÍą (Soft Water) â´ÂˇŇáӨѴľÇˇ˘Í§á˘ç§á˘ÇąĹÍ ¤ÇŇÁ˘Řčą µĐˇÍą ĘŇĂÍÔą·ĂŐÂěĹĐĹŇÂáĹФĹÍĂŐą ĂÇÁ·Ńé§ÍÔÍÍąµčҧć

- ĂĐşş Ultra Deionized (UDI) Water ŕ»çąĂĐşşˇŇĂ·Ó¤ÇŇÁĘĐÍŇ´ąéÓÍčÍą (Soft Water) ăËéŕ»çąąéÓ·ŐčÁŐ¤ÇŇÁşĂÔĘŘ·¸ÔěĘ٧ â´Â·ÓˇŇáӨѴÍÔÍÍąµčŇ§ć ·ŐčŕËĹ×ͨҡˇŇĂ·Ó¤ÇŇÁĘĐÍŇ´ąéÓŕş×éͧµéą ÍŐˇ·Ńé§Âѧ¦čҨŘĹÔą·ĂŐÂě·Őč»Đ»ąÁҡѺąéÓ ŕľ×čÍăËéä´éąéÓ¤ÇŇÁşĂÔĘŘ·¸ÔěĘ٧µĂ§µŇÁÁҵðҹ㹡ŇĂĽĹԵǧ¨ĂĂÇÁ «Öč§â´Â»ˇµÔ ČŮąÂěĎ ĘŇÁŇöĽĹÔµąéÓĘĐÍŇ´ËĂ×Í Ultra Deionized (UDI) Water ä´é¶Ö§ 3.5 Ĺ١şŇȡěŕÁµĂµčÍŞŃčÇâÁ§ áĹĐÁŐ¤čҤÇŇÁµéŇą·ŇąäÁčµčÓˇÇčŇ 18 ŕÁˇĐâÍËěÁ-ŕ«ąµÔŕÁµĂ

ËĹѧˇŇĂÍ͡ẺĽŃ§Ç§¨ĂŕĘĂç¨ĘÔéą ĽŮéÍ͡Ẻ¨ĐăŞé¤ÍÁľÔÇŕµÍĂěŞčǵĂǨĘÍşÇčҼѧŔŮÁÔǧ¨Ă (layout) ąŃ鹶١µéͧµŇÁˇ®ˇŇĂÍ͡Ẻ ˇ®·Ň§äżżéŇ áĹĐÁŐ¤ÇŇÁĽÔ´ŕľŐéÂą¨ŇˇáĽąŔŇľŕ¤éŇĂčҧ (schematic) ËĂ×ÍäÁč ËҡÁŐ¤ÇŇÁĽÔ´ľĹŇ´ËĂ×ÍĽÔ´ŕľŐéÂą ¨Ř´ĽÔ´ŕËĹčŇąŃéąµéͧä´éĂŃşˇŇĂáˇéä˘ ˇčÍąĘč§áżéÁ˘éÍÁŮżѧǧ¨ĂĂÇÁä»ăËéâç§Ňą·ÓËąéҡҡ (mask) ĘÓËĂŃşăŞéĽĹÔµŕ»çąäÁâ¤ĂŞÔ»µčÍä»

ŕ·¤âąâĹÂŐËĹѡ·ŐčăŞé㹡ŇĂÍ͡ẺáĹĐĽĹԵǧ¨ĂĂÇÁąŃéąä´éáˇč ŕ·¤âąâĹÂŐ CMOS «Ö觨ĐÁŐ˘ąŇ´ŕĹçˇĹ§ŕĂ×čÍÂć ăąĘčÇą˘Í§ TMEC ąŃéąáąÇâąéÁ¨Đŕąéąä»·Ň§ low power/low voltage «Ö觨ĐăŞé§Ňą·Ň§´éŇąŕ«ąŕ«ÍĂě

ăąĘčÇąÍ×蹢ͧ෤âąâĹÂŐ·ŐčăŞéľŃ˛ąŇǧ¨ĂĂÇÁąŃ鹹͡¨ŇˇˇŇĂĽĹÔµâ´ÂăŞéŕ·¤âąâĹÂŐ CMOS áĹéÇÂѧĘŇÁŇöľŃ˛ąŇǧ¨Ăâ´ÂăŞéŕ·¤âąâĹÂŐŕÍżľŐ¨ŐŕÍ (Field Programmable Gate Array) â´ÂˇŇĂ·´ĘÍşµéąáşşÇ§¨ĂşąşÍĂ촾ѲąŇˇčÍą·Őč¨ĐÍ͡ẺăąĂĐ´ŃşĽŃ§ŔŮÁÔµčÍä» ŕŞčąşÍĂě´ Xilinx Spartan-3 ĂͧĂѺǧ¨Ăä´é¶Ö§ 1.6 Ĺéҹࡵ áĹĐşÍĂ촾ѲąŇŕÍżľŐ¨ŐŕÍ Virtex-5

-

ŕ¤Ă×čͧÁ×ÍáĹĐÍŘ»ˇĂłě

ŕ¤Ă×čͧÁ×ÍËĹѡ·Őč¨Óŕ»çąăąˇŇĂ´ÓŕąÔąˇŇĂÇÔ¨ŃÂáĹоѲąŇä´éáˇč

- ¤ÍÁľÔÇŕµÍĂě¤ÇŇÁŕĂçÇĘ٧ĘÓËĂŃşˇŇĂÍ͡ẺáĹШÓĹͧǧ¨Ă «Ö觷ӧҹÍÂŮčşąĂĐşş»ŻÔşŃµÔˇŇĂ Linux áĹĐ Solaris

- «ÍżµěáÇĂěĘÓËĂŃşÍ͡Ẻǧ¨ĂĂÇÁ (Electronic Design Automation: EDA) »ĂСͺ´éÇ Cadence IC Design Software, Xilinx FPGA Design, Tanner Tools

- ŕ¤Ă×čͧÁ×ÍÇŃ´áĹĐ·´ĘÍş

- ¤Ô·ŕ·¤âąâĹÂŐĘÓËĂŃşˇŇĂÍ͡Ẻ (Design kit) ŕŞčąŕ·¤âąâĹÂŐ CMOS 0.8/0.5/0.35/0.25/0.18um

şĂÔˇŇĂÍ͡ẺäÍ«Ő (IC Design Services)

şĂÔˇŇĂÍ͡ẺäÍ«Ő ăËé¤Ó»ĂÖˇÉŇ㹡ŇĂÍ͡Ẻǧ¨Ă şŘ¤ĹҡâͧČŮąÂě ¨ĐăËé»ĂÖˇÉŇăą´éŇąˇŇĂÍ͡Ẻǧ¨ĂĂÇÁµčŇ§ć ˇŇĂŕĹ×͡ăŞé«ÍżµěáÇĂě·ŐčŕËÁŇĐĘÁˇŃş§Ňą·Őč¨ĐăŞé áĹĐĂŃşÍ͡Ẻǧ¨Ă ˇŇèÓĹͧǧ¨Ă ˇŇĂŕ˘Ő¹ǧ¨Ă´éÇÂŔŇÉŇŞŃéąĘ٧ VHDL/Verilog ˇŇĂĘѧŕ¤ĂŇĐËěǧ¨Ă áĹСŇĂ·Óµéąáşş´éÇ FPGA

şĂÔˇŇĂŞčͧ·Ň§ˇŇĂ·ÓµéąáşşäÍ«Ő (Thai Chip Prototype Services)

şĂÔˇŇĂŞčͧ·Ň§ˇŇĂ·ÓµéąáşşäÍ«Ő ČŮąÂě¨ĐŞčÇ´ÓŕąÔąˇŇĂ㹡ŇõԴµč͡ѺĽŮéĽĹÔµáĽčąÇ§¨ĂĂÇÁ «Ö觷ҧČŮąÂěÁŐ˘é͵ˇĹ§ľÔŕČɡѺşĂÔÉŃ·ĽŮéĽĹÔµµčŇ§ć ·ÓăËéĘŇÁŇö·ÓµéąáşşÇ§¨ĂĂÇÁ»ĂÔÁŇłµčÓä´éăąĂҤҷŐčµčÓŧÁҡ â´ÂˇŇĂĂÇÁẺǧ¨ĂĂÇÁ¨ŇˇËĹŇ·Őčŕ˘éŇ´éÇ¡ѹ áĹĐĘĂéҧŧşąËąéҡҡÍŃąŕ´ŐÂǡѹ ŕ·¤âąâĹÂŐ·ŐčĘŇÁŇö·Óä´éä´éáˇč CMOS, BiCMOS SiGe áĹĐ GaAs

˝ÖˇÍşĂÁ´éŇąˇŇĂÍ͡ẺäÍ«Ő

˝ÖˇÍşĂÁ´éŇąˇŇĂÍ͡ẺäÍ«Ő ČŮąÂěä´é¨Ń´ˇŇý֡ͺĂÁËĹѡĘٵà ´éŇąˇŇĂÍ͡Ẻǧ¨ĂĂÇÁµčҧć ŕ»çą»ĂĐ¨Ó ŕľ×čͻپ×éą°Ňąăą´éŇąˇŇĂÍ͡Ẻǧ¨ĂĂÇÁ áĹĐŕľÔčÁľŮą»ĂĐĘşˇŇĂłěăËÁčć ăËéˇŃşąŃˇÍ͡Ẻǧ¨ĂĂÇÁ â´Â·ŐčËĹѡĘٵ÷Őč¨Ń´˘Ö鹤ĂÍş¤ĹŘÁ ľ×éą°ŇąˇŇĂÍ͡Ẻǧ¨ĂĂÇÁ (IC Layout Design) ˇŇĂÍ͡Ẻǧ¨Ă´éÇÂŔŇÉŇ VHDL áĹĐ Verilog ˇŇĂÍ͡Ẻǧ¨Ă´éÇ FPGA ˇŇĂÍ͡Ẻǧ¨ĂĂÇÁÍĐąŇĹç͡ ˇŇèÓĹͧÍŘ»ˇĂłěˇÖ觵ŃÇąÓáĹСŇèÓĹͧˇĂкǹˇŇĂĽĹÔµÍŘ»ˇĂłěˇÖ觵ŃÇąÓ

Document

Document